반도체 기본 개념과 공정 과정들을 한눈에 정리해 보았습니다!

투자 공부하실 때 참조해 보세요ㅎㅎ

1. 반도체 산업의 기본 개념

반도체는 데이터를 저장하는 역할을 하는 메모리 반도체(DRAM, NAND)와 연산/논리를 돕는 비메모리 반도체로 구분된다. 메모리 반도체는 데이터를 기억하는 역할로, 전원 공급 시 데이터 보관 유/무에 따라서 RAM(;DRAM)과 ROM(;NAND)으로 분류되고 메모리 반도체 이외의 제품은 모두 비메모리 반도체로 통칭할 수 있다.

메모리부터 하나씩 살펴보자.

① DRAM

- DRAM은 빠른 속도로 데이터를 읽고 쓸 수 있으나, 전기가 지속적으로 공급돼야 데이터가 사라지지 않는다. 예를 들면 DRAM은 공부하는 사람(CPU)이 사용하는 책상 같은 존재. (퇴근하면 진행 중이던 작업이 사라짐)

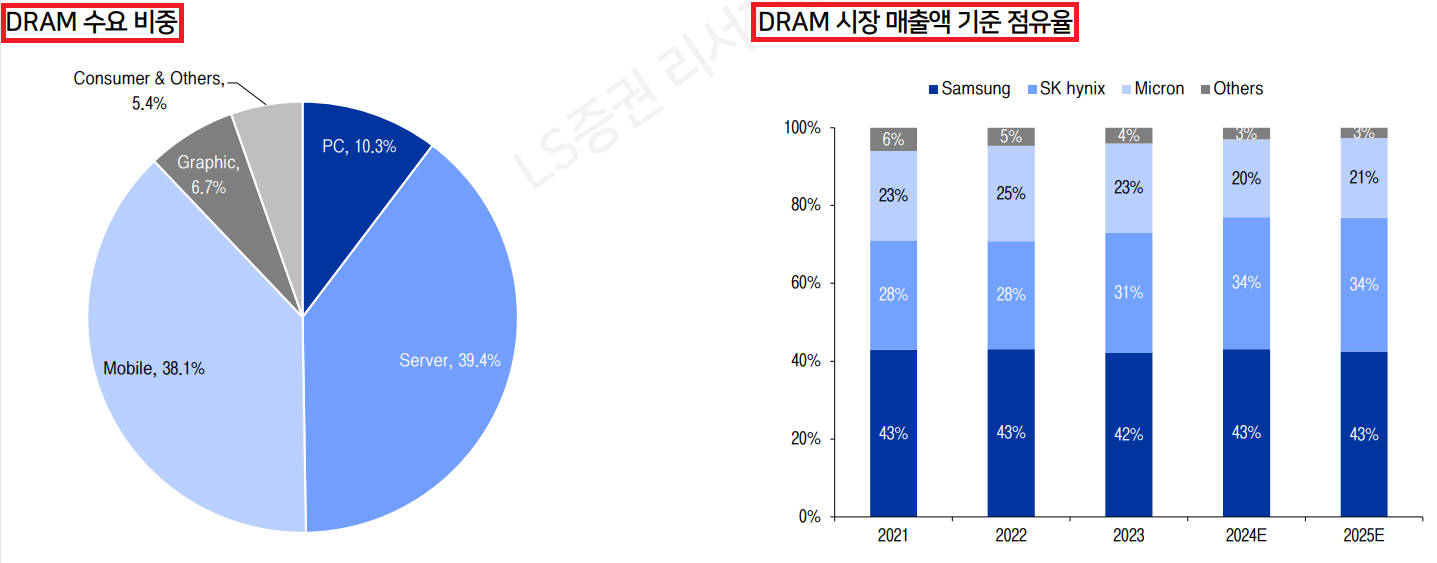

주요 수요는 서버 40%, 모바일 40%, PC 10%, 그 외 10%이며,

주요 공급자는 삼성전자 43%, SK하이닉스 34%, Micron 20%, 기타(CXMT 등) 3%으로 과점 시장이다.

② NAND

- NAND는 DRAM에 비해 속도가 느리지만 전기가 공급되지 않아도 데이터가 유지된다. 예를 들면 NAND는 일하는 사람(CPU)이 일을 마치고 서류를 보관하는 책장 같은 존재. (퇴근해도 작업이 유지됨)

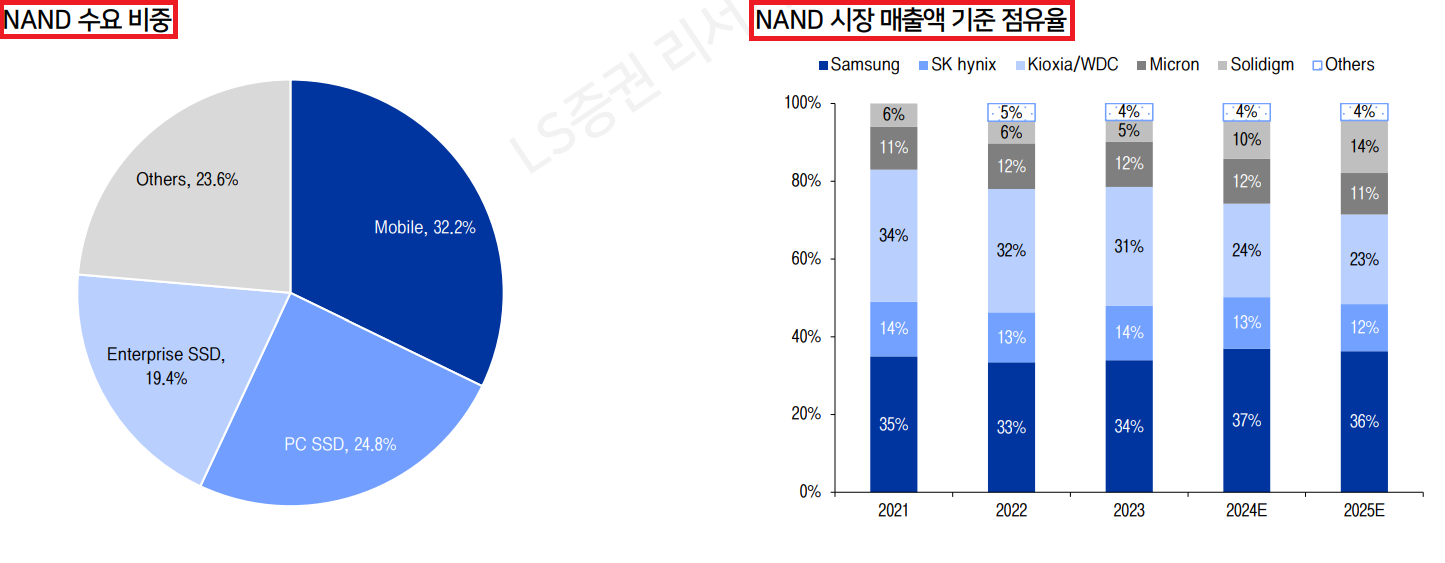

주요 수요는 모바일 32%, PC 25%, Server 20%, 그 외 25%이며,

주요 공급자는 삼성전자 37%, Kioxia/WDC 24%, SK하이닉스 13%, Micron 12% 등으로 아직 경쟁 시장이다.

따라서 DRAM(과점시장) 대비 NAND(경쟁시장)의 수익성이 비교적 낮다.

③ 시스템 반도체(비메모리) – CPU & GPU & AP

- CPU(Central Processing Unit): 컴퓨터 중앙처리장치. 복잡한 한 개의 데이터 처리에 장점.

→ Datacenter, PC 등에 쓰임.

- GPU(Graphics Processing Unit): 그래픽 처리 장치. 간단한 다수의 데이터 처리에 장점.

→ 게임용 PC, AI Server 등에 쓰임.

- AP(Application Processor): SoC(System on Chip) 제품으로 CPU, GPU 등을 하나의 칩에 통합한 제품.

→ 공간 제약이 있는 스마트폰 등에 쓰임.

메모리 반도체는 비메모리에 비해 상대적으로 만들기가 쉽다. 따라서 소품종 대량생산이 가능하고 분업화에 대한 필요성이 적은 반면, 비메모리 반도체는 만들기도 어렵고 설계도 까다롭다. 다품종 소량생산으로 진행되며 분업화가 필수적이다.

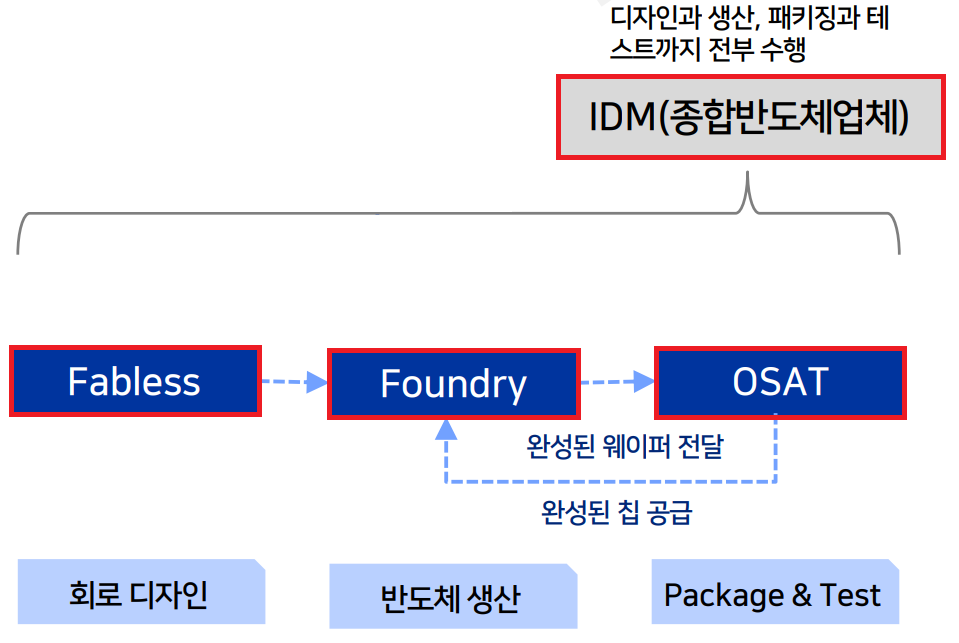

이러한 이유로 반도체 산업의 밸류체인이 아래와 같이 나뉜다.

1) 설계 전문 업체 (팹리스, Fab-less)

- 팹리스, 즉 공장이 없다. 반도체 설계만을 담당하며 설비 투자가 불필요하다. 미국의 엔비디아, 퀄컴이 해당한다.

2) 위탁제조업체 (파운드리, Foundry)

- 생산만을 담당하며, 대규모 Capex투자를 통한 Capa 및 수율 확보가 핵심이다.

3) 종합 반도체 업체 (IDM, Integrated Device Manufacturer)

- 설계와 생산 모두를 같이 담당한다. 삼성전자, SK하이닉스, Micron, Intel이 모두 여기에 속한다.

4) 후공정 업체(OSAT: Outsourcing Semiconductor Assembly and Test)

- 반도체 공정 중 후반부인 후공정, 패키징 및 테스트 공정만을 담당하는 외주업체이다.

▶여기서 메모리는 한 회사가 한 번에 다 할 수 있기 때문에, 메모리 업체들은 주로 IDM이며 비메모리가 팹리스, 파운드리, OSAT로 구분되어 있다.

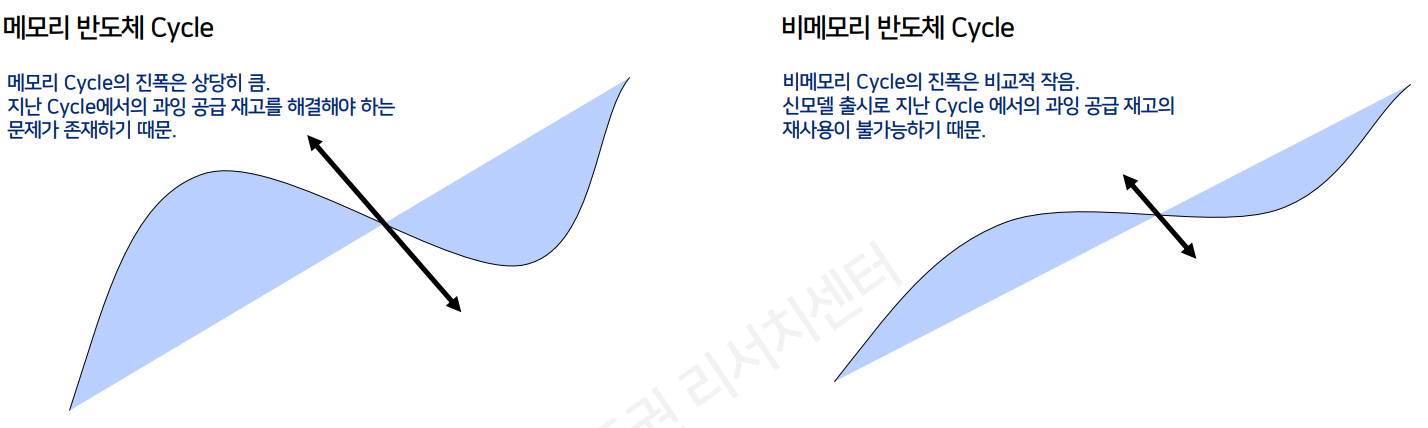

▶ 메모리 산업은 이러한 이유로 IDM 업체 몇 군데가 수요와 공급을 일일이 예측하여 시장에 대응하는 '공장' 산업이기 때문에 시스템반도체(비메모리) 산업과 달리 Cycle이 생기게 된다.

- 메모리는 소품종 대량 생산으로 지난 과잉 공급 때 남은 재고를 판매할 수 있지만 시스템반도체의 경우 잦은 스펙 업그레이드로 이전 세대 제품을 재고로 활용이 불가능하고, 수요 예측에 있어서도 메모리는 범용제품으로 전체 테크 수요를 예측해야 하지만 비메모리 업체들은 자신의 제품군에 대해서만 예측이 필요하여 비교적 쉽다. 이에 국내 메모리 업체들은 비메모리로의 사업 확대를 통한 실적 안정성을 추구하는 전략을 추진하고 있다.

2. 반도체 공정 정리

반도체 제작 과정은 전공정과 후공정으로 나뉘게 된다.

쉽게, 전공정은 반도체를 만드는 과정이고 후공정은 만든 반도체를 검사하고 포장하는 과정이다.

Wafer 생산 이후 진행되는 회로 및 구조 형성 공정을 전공정이라 칭하고, 순서는 산화공정 → 포토(노광) 공정 → 식각공정 → 박막(증착) 공정 → 금속 배선 공정으로 진행다. 이후, 전공정이 끝나고 가공된 웨이퍼를 잘라 각각의 칩을 테스트, 패키징을 거쳐 완성품으로 만드는 과정을 ‘후(後)’공정이라고 한다. 기존 후공정은 기술보다는 노동집약적 산업으로 부가가치가 높지 않았으나, 최근 공정전환의 난이도 증가로 전공정 과정이 한계에 부딪힘에 따라 후공정의 중요성이 증가하고 있다.

▶공정을 본격적으로 설명하기 전, 이해를 위해 주요 용어를 간단히 정리해 보자.

- 웨이퍼(Wafer): 실리콘(모래에서 추출한 규소)으로 만든 반도체의 기반. 12인치와 8인치(레거시) 웨이퍼를 사용함.

- 다이(Die): 반도체 칩의 회로가 구현되는 영역. 칩은 후공정까지 완료된 반도체를 의미.

- 넷다이(Net Die): 웨이퍼 내에서 생산 가능한 Die의 숫자

- 수율(Yield): 전체 넷다이 중 양산품(Good Die)의 비율

- Capa: 반도체 업계에서는 주로 1달에 공정 투입하는 Wafer 숫자로 Capa를 표기 Ex) 10K/m

- 나노미터(nm): 반도체 회로 선폭에 사용되는 단위. (1nm=1/10억 m), 다만 최근에는 실제 선폭의 길이 축소보다는 다양한 방식으로 성능을 개선시키며 nm는 마케팅적 의미가 강해짐.

* 반도체 미세화의 장점: ① 고성능(동일 면적 더 많은 회로), ② 저전력(동일 회로 더 작은 칩), ③ 수율 향상

- 회로 설계: 트랜지스터 등의 소자 모델을 바탕으로 회로 디자인 진행하는 과정, CAD 시스템으로 실제 Wafer 위에 그려질 회로 패턴과 전자회로를 설계하는 것

- 마스크(Mask) 설계: 설계한 회로 패턴을 유리판에 새기는 과정, 규칙에 맞도록 반도체 소자/배선을 그림으로 그려내고 배치하는 것을 레이아웃(Layout)이라고 하며, 레이아웃을 만드는 작업을 마스크 설계라고 함

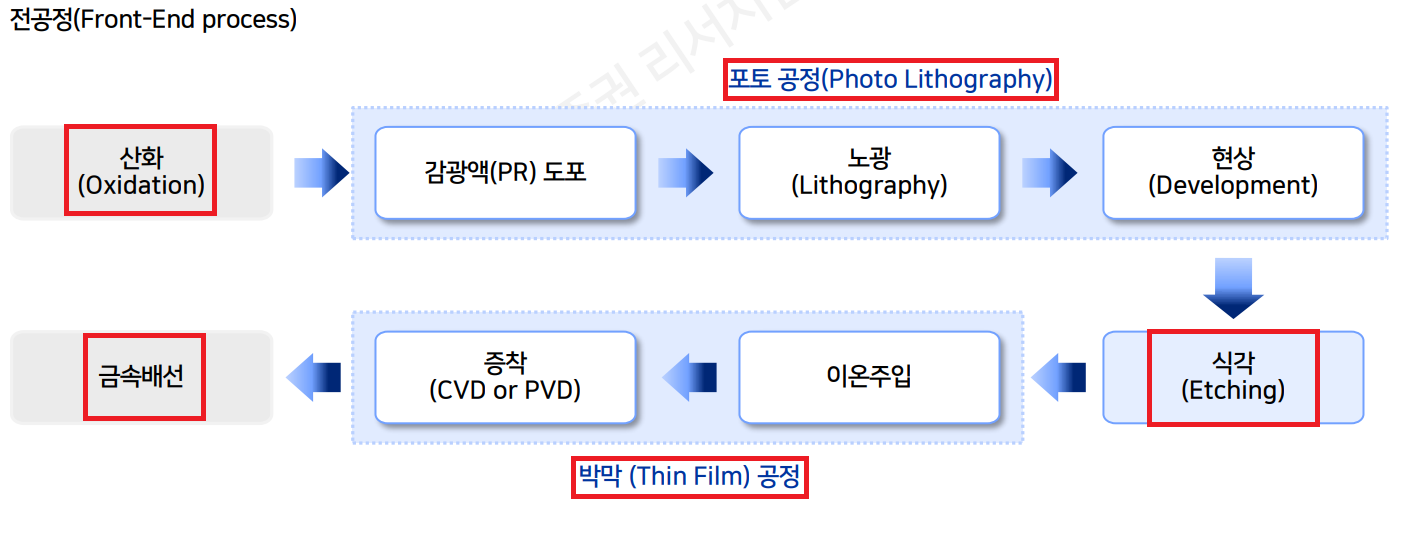

① 전공정 과정

산화 - 포토 - 식각- 증착 - 배선

1) 산화 공정

: 웨이퍼 실리콘 표면의 산화를 통해 얇은 막을 씌우는 과정.

고온(800~1200도)에서 산소나 수증기를 Wafer 표면에 뿌려, 얇고 균일한 실리콘 산화막을 형성시키며, 형성된 산화막은 공정 시 발생하는 불순물로부터 실리콘 표면을 보호함. 산화공정은 크게 건식(산소) 산화 반응과 습식(수증기) 산화로 나뉘게 된다.

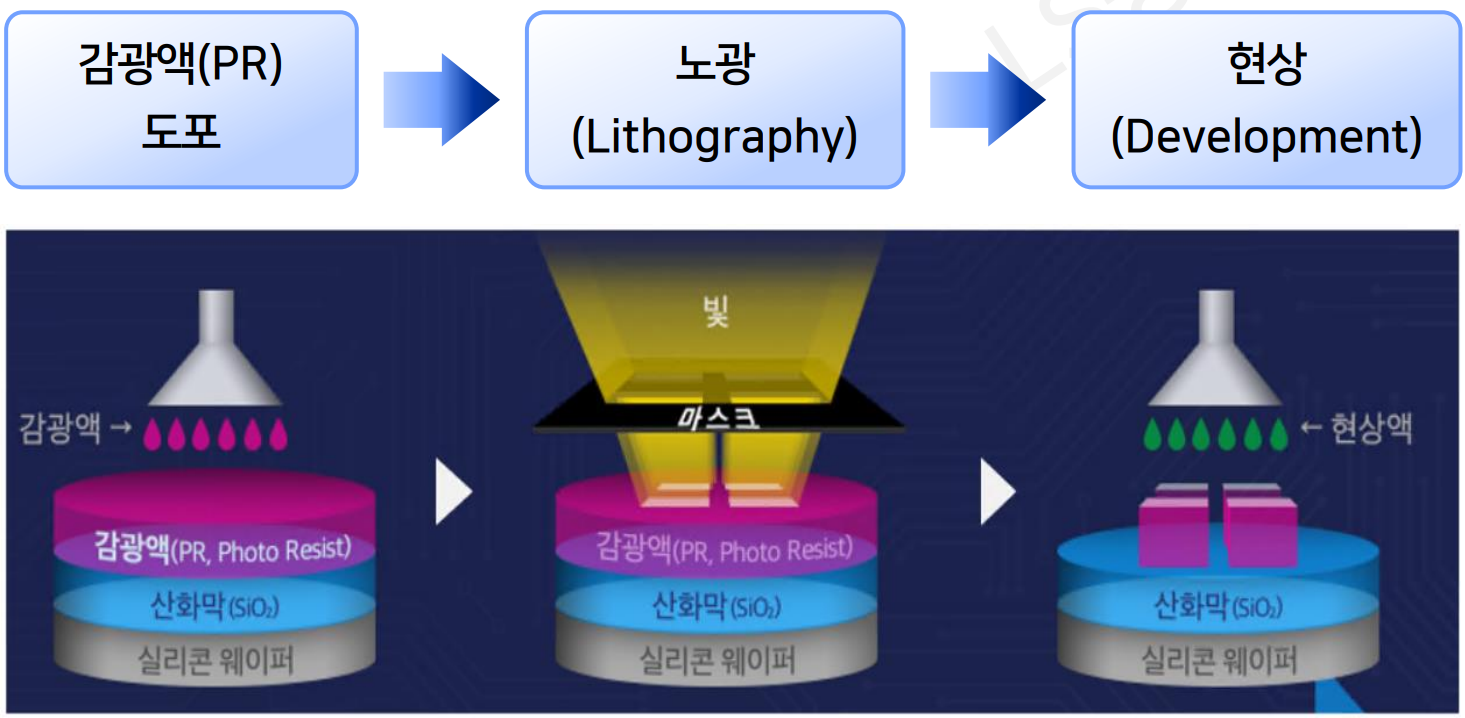

2) 포토 공정

: 웨이퍼 위에 회로를 구현하는 과정.

반도체 제조 공정에서 공정 비용의 약 35%, 공정시간의 60% 이상을 차지하는 핵심 기술로 가장 난도가 높고 중요한 공정. 감광액 도포-노광-현상의 3단계를 거친다.

- 감광액 도포(PR coating, Photo-Resist coating): 웨이퍼 표면에 감광액을 균일하게 도포한 후, 빠르게 회전하여 균일한 두께의 얇은 막 형성

- 노광(Lithography or Exposure): 노광장비를 사용하여 마스크(Mask)에 그려진 회로 패턴에 빛을 통과시키고 회로 패턴 사진을 찍는 과정.

- 현상(Development): 웨이퍼에 현상액을 뿌려가면서 노광된 영역과 노광되지 않은 영역을 선택적으로 제거하며 패턴을 만드는 과정

이때, 노광 광원 종류에 따라 파장이 다르게 되고 파장이 짧을수록 미세회로 구현이 가능하다. 현재는 EUV (Extreme Ultraviolet) 광원이 파장이 가장 짧으며 14nm이하 미세 공정부터는 EUV 장비가 필요하다. EUV를 사용하면 노광 공정의 횟수도 확연히 줄일 수 있다.

3) 식각 공정

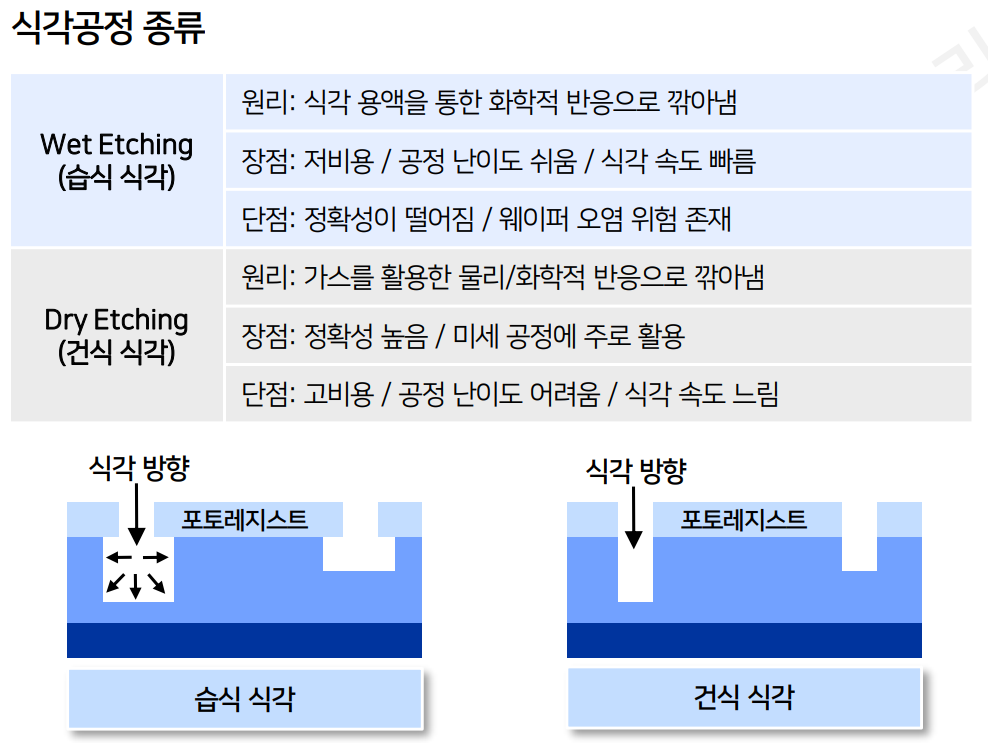

: 노광 공정에서 형성한 패턴을 따라 산화막을 깎아내는공정. 깎아내는 방식은 1) 습식과 2) 건식으로 나뉘게 된다.

습식은 용액을 통해 화학적 반응으로 깎아내는 반면, 건식은 가스를 이용해 물리적으로 깎아내는 방식이다.

습식은 빠르고 저렴하나, 정확성이 떨어지고 건식은 정확성이 높은 대신 어렵고 비용이 많이 든다. 건식이 발전된 방식이다.

4) 증착 공정

: 웨이퍼 위에 원하는 물질을 박막 두께로 올려서 전기적 특성을 갖게 하는 공정.

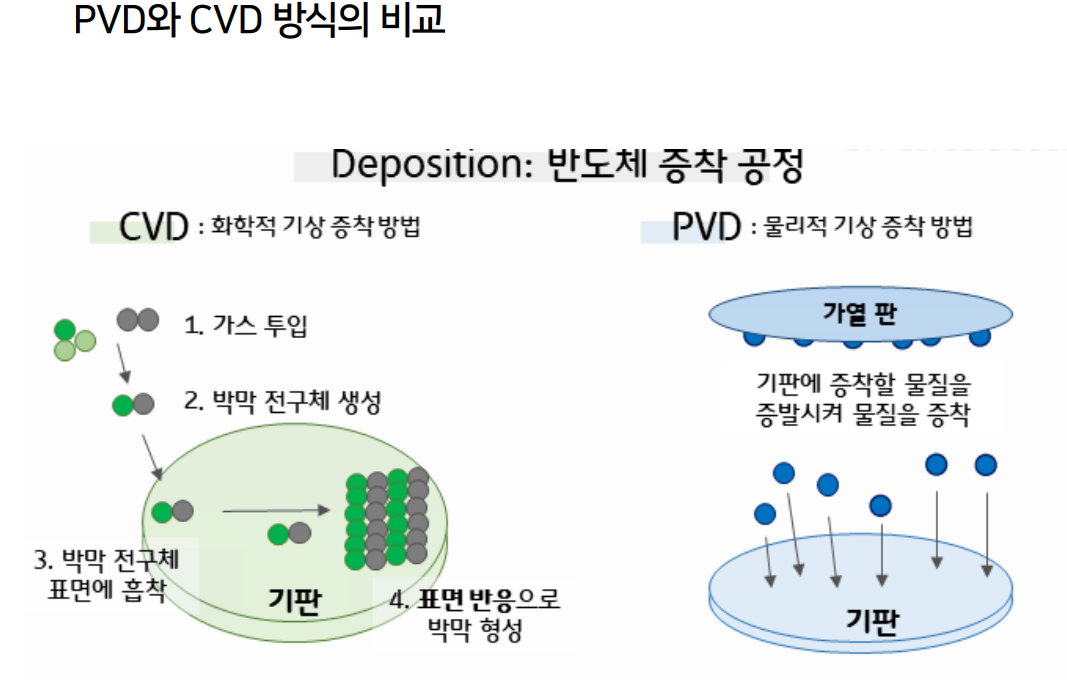

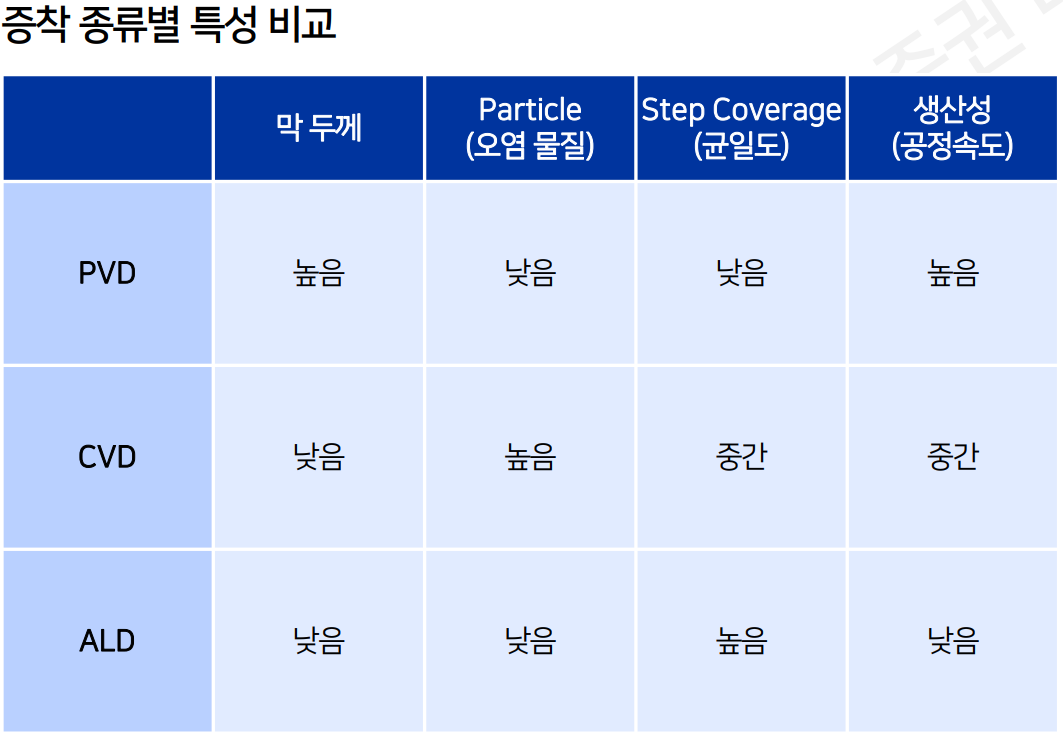

방식은 크게 PVD/CVD/ALD로 나뉘는데, 현재 CVD를 주로 사용하고 있으며 ALD로 공정 전환 중에 있다.

- PVD(Physical Vapor Deposition): 물리적 증착 방법. 주로 금속 박막의 증착에 사용됨. 증착하고자 하는 물질에 직접적으로 에너지를 인가하고 입자를 웨이퍼까지 이동시켜 증착하는 방식.

- CVD(Chemical Vapor Deposition): 화학적 증착 방법. 챔버 안에 반응할 가스(Chemical)를 주입하고 가스에 에너지를 인가하여 화학반응 유도 후 증착. PVD 대비 박막의 균일도가 좋음

- ALD(Atomic Layer epitaxy Deposition): CVD와 유사한 화학적 방식이지만 한 사이클 당 한 개의 원자층만 쌓이게 함.

* CVD- 한꺼번에 막이 쌓이게 함/ALD-순서에 맞추어 차례로 소스를 공합하여 한 층 씩 쌓이게 함

막 균일도가 높고 나노 단위의 섬세한 코팅이 가능하지만 공정 속도가 느리다는 단점이 있음

5) 배선 공정

: 앞선 주요 공정들로 소자, 즉 트랜지스터가 형성되지만 이 자체로만은 작동이 되지 않는다. 소자들은 전원공급 및 소자들 간 연결이 필요한데 이를 이어주는 회로를 구성하는 것이 금속 배선 공정이다. 배선에 알루미늄 소재를 사용하면 공정이 쉬우며 가격이 저렴하지만 내구성이 약하고, 구리 소재를 사용하면 내구성이 좋지 공정이 어려워진다는 단점이 있다.

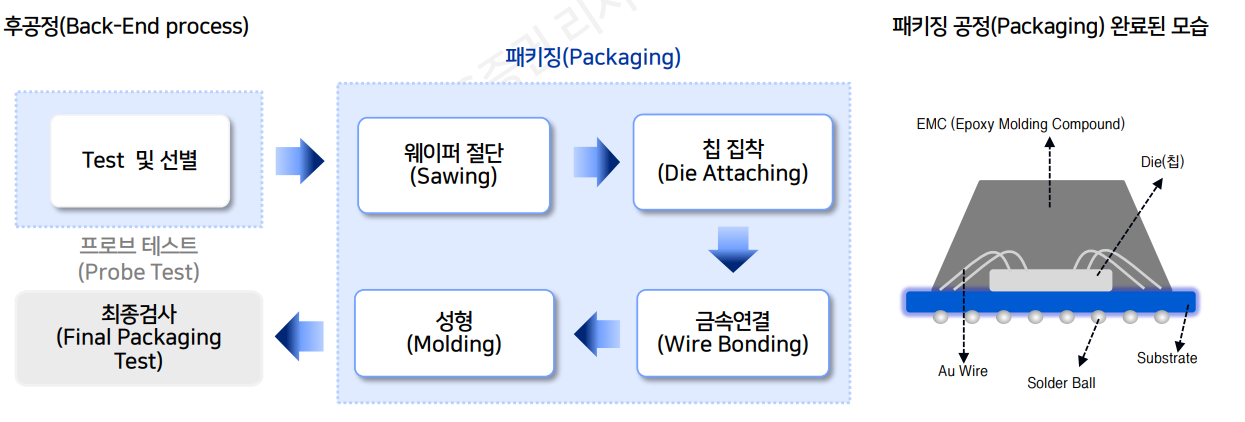

②후공정 과정

후공정은 전공정이 끝나고 가공된 웨이퍼를 잘라 각각의 칩을 테스트, 패키징을 거쳐 완성품으로 만드는 과정이다.

웨이퍼 테스트 → 백그라인딩 → 싱귤레이션 → 본딩 → 몰딩 → 마킹 → 솔더볼 마운트 → 패키징 테스트

1) 웨이퍼 테스트: 개별 Chip으로 자르기 전 Wafer 상태로 특성과 품질을 테스트하는 과정.

2) 싱귤레이션: 웨이퍼 위의 칩을 개별로 나누기 위해 Dicing(다이싱)/Sawing(쏘잉)을 가하는 공정.

3) 본딩: 다이싱 공정 후 웨이퍼에서 분리된 칩과 패키지 기판(Package Substrate, 리드프레임 혹은 PCB)을 접합하는 과정

4) 몰딩: 반도체 칩을 외부 환경으로부터 보호하기 위해 특정 물질로 감싸주는 단계.

5) 마킹: 칩 표면 위에 반도체 종류, 제조사 등 제품에 대한 정보와 고객이 원하는 특정 표식을 새기는 작업

6) 솔더볼 마운트: 칩과 기판을 연결하여 전기적 신호를 전달하는 솔더볼을 부착하는 단계.

7) 페키징 테스트(파이널 테스트): 제품을 출하하기 전 최종적으로 전기적인 특성을 검사한다고 하여 파이널 테스트(Final Test)라고 부름.

▶ 전공정의 한계로 후공정이 부각되고 있음.

오랜 기간 동안 칩의 성능은 전공정 발전 위주였으나 개발 비용의 급격한 증가와 성능 개선의 한계에 도래. 후공정 기술(범프, 기판, 구조 등)의 발전을 통해 반도체의 성능 향상을 도모하기 시작함. 시스템 반도체에서는 FO-WLP, FO-PLP, CoWoS, Hybrid Bonding 등의 기술이 적용되는 중.

반도체 공부하실 때 정말 좋은 보고서입니다!

꼭 한번 읽어보시길 권해드립니다ㅎㅎ

맨 아래 자료 첨부해 두었습니다.

[반도체, 241106, LS증권, 반도체 톺아보기]